Für eine effiziente digitale Zukunft und technologische Souveränität erweisen sich Hoch- und Höchstleistungsrechner von enormer Bedeutung. Beim so genannten High Performance Computing (HPC) erfassen Rechenzentren riesige Datenmengen und führen damit komplexe Berechnungen durch. Zum Einsatz kommt HPC also immer dort, wo rechenintensive Operationen in Hochgeschwindigkeit erforderlich sind: Dies kommt besonders der Wissenschaft für das Erstellen aufwändiger Simulationen und Algorithmen zugute, aber auch bei der Optimierung von Verkehr, Logistik, Industrie oder Präzisionsmedizin finden die Superrechner bereits heute Anwendung. Dabei ist HPC nur eine von vielen zukunftsträchtigen Anwendungen, deren Grundlage Leistungsfähigkeit und Effizienz sind.

Um diese hohen Anforderungen zu erfüllen, sind neue Verbindungstechnologien entscheidend. Die Idee dahinter ist: Je kleiner der Pitch, also der Abstand zwischen elektronischen Kontaktpunkten, desto mehr Transistoren und Schaltkreise können auf einem Chip untergebracht werden, was wiederum zu einer höheren Leistungsfähigkeit führt. Bisher haben sich bei Flip-Chip-Anwendungen die Kupfer-Bumps mit Lot als Standardtechnologie erwiesen. Bei zunehmender Miniaturisierung stößt dieses Verfahren jedoch an seine Grenzen, da das Lotmaterial austreten und zu Kurzschlüssen führen kann.

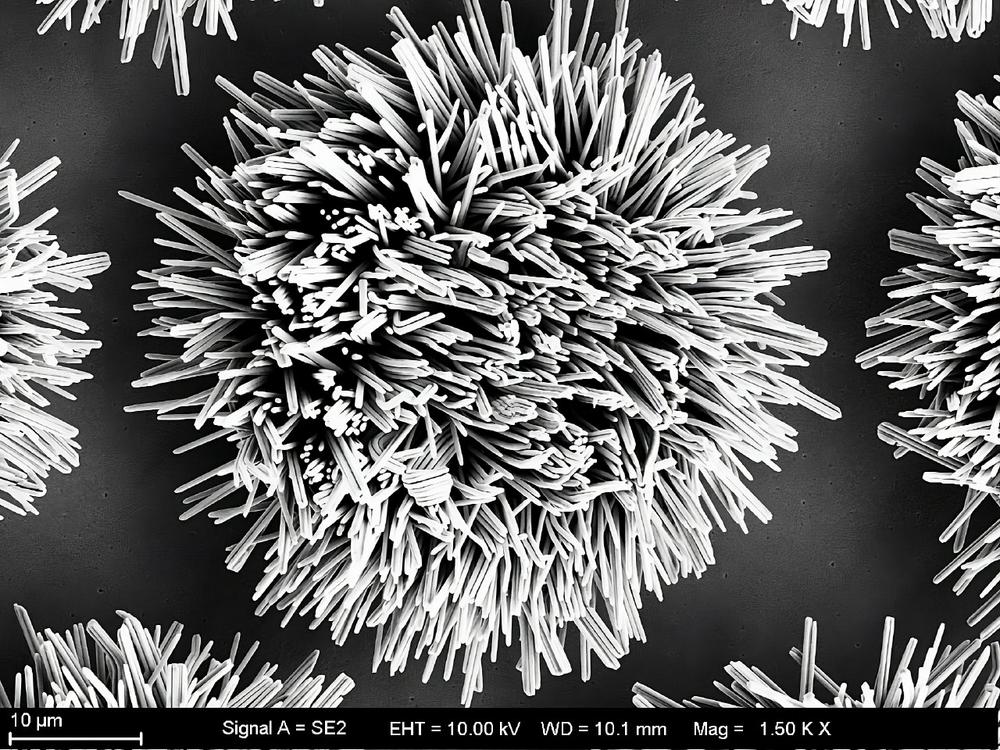

Um innovative Alternativen zu finden, forscht Jun.-Prof. Dr.-Ing. Iuliana Panchenko mit ihrem Team am Fraunhofer IZM-ASSID an neuen Verbindungstechnologien für kleine Kontaktierungen unter 10 Mikrometern. Im Rahmen des Fraunhofer-geförderten SME-Projekts „NanoInt“ entwickelte das Team gemeinsam mit Partner*innen aus Wissenschaft und Industrie eine vielversprechende Lösung mit Nanodrähten aus Kupfer und evaluierte das Verfahren erfolgreich für die Anwendung auf 300 Millimeter breiten Silizium-Wafern.

Im Vergleich zu anderen Ansätzen wie dem Löten mit Kupfer oder Lot Bumps, dem Hybrid- oder Kompressions-Bonden bietet die direkte Kupferverbindung mit Nanodrähten einige Vorteile. Diese Verbindungstechnologie toleriert dank des Steckprinzips (Nanodraht-zu-Nanodraht) mehr Höhenvariationen, benötigt keine weiteren Metalle, bietet mehr Designfreiheit und gewährleistet gute mechanische Festigkeit. Zudem kann die Kontaktierung schon unter Raumtemperatur und bei geringem Bonddruck realisiert werden. Dadurch ist die ressourcenschonende Technologie auch für Low-Temperature-Bonding und somit für temperaturempfindliche und dünne Chips geeignet.

In der ersten Projektphase lag der Fokus darauf, das Wachstum der Nanodrähte an den Verbindungstellen auf dem ganzen 300 mm Wafer so homogen wie möglich zu realisieren. Das Forschungsteam nutzte dafür Membranen, die mit feinen Poren versehen sind. Der Porendurchmesser ist entscheidend für die Dicke der Nanodrähte und kann zwischen 100 nm und 1 µm variiert werden. Um leitfähige und zuverlässige Verbindung zu erzeugen, musste die Porendichte vorab evaluiert werden. In einem galvanischen Prozess wachsen die Kupfer-Nanodrähte in den Poren der Membran. Durch Prozessoptimierungen wurde eine Variation der Nanodraht-Höhen von circa 20 Prozent auf dem gesamten Wafer erreicht. Zusätzlich hat das Forschungsteam eine Prozessabfolge entwickelt, mit der die Nanodrähte während der Ätzprozesse geschützt werden, so dass die leitfähige Kupfer-Keimschicht auf dem Wafer entfernt werden kann.

Um die Verbindungstechnologie applikationsnah zu evaluieren, demonstrierten die Forschenden die Integration des Verfahrens in die industrielle Prozessierungskette. Hierfür wurden die optimalen Parameter für das weitere Assembly solcher Aufbauten identifiziert und unter besonderer Prüfung der Reproduzierbarkeit, Homogenität, mechanischer Festigkeit und Industrietauglichkeit umgesetzt.

Am Ende des Projekts demonstrierten die Partner*innen einen 300 mm Silizium-Wafer mit gleichmäßigen Nanodrähten als Bumps und einen Chip-zu-Chip-Aufbau mit Nanodraht-Verbindungen. Damit zeigen sie die erfolgreiche Systemintegration für 2,5D und 3D-Aufbauten ohne den Einsatz von Flussmitteln. Im Ergebnis wird die Technologie bereits für die Industrie angeboten. In anstehenden Forschungsprojekten sollen die Kontakte sogar von 10 auf unter 5 Mikrometer schrumpfen. Perspektivisch lassen sich die Anwendungsbereiche der Nanodraht-Verbindungstechnologie ausweiten, so dass sie für komplexe Packages mit Fine-Pitch und großflächigen Kontakten einsetzbar wird.

Weitere Partner*innen im Projekt NanoInt sind das NanoWired GmbH, Fraunhofer IMWS, die IAVT der TU Dresden.

(Text: Olga Putsykina)

Hoch integrierte Mikroelektronik ist allgegenwärtig und bleibt doch fürs bloße Auge meist unsichtbar. Seit über 30 Jahren unterstützten wir an den Standorten Berlin, Dresden und Cottbus Startups sowie mittelständische und internationale Großunternehmen mit Technologietransfer für intelligente Elektroniksysteme der Zukunft. Das Fraunhofer IZM deckt mit vier zentralen Technologie-Clustern eine große Bandbreite aus den Bereichen Quantentechnologie, Medizin-, Kommunikations- und Hochfrequenztechnik ab. Mit unserer weltweit führenden Expertise bieten wir unseren Kund*innen kostengünstige Entwicklung und Zuverlässigkeitsbewertung von Electronic Packaging Technologien sowie maßgeschneiderte Systemintegration auf Wafer-, Chip- und Boardebene.

Fraunhofer-Institut für Zuverlässigkeit und Mikrointegration IZM

Gustav-Meyer-Allee 25

13355 Berlin

Telefon: +49 (30) 46403-100

Telefax: +49 (30) 46403-111

http://www.izm.fraunhofer.de

Presseansprechpartner

Telefon: +49 (30) 46403-279

Fax: +49 (30) 46403-650

E-Mail: georg.weigelt@izm.fraunhofer.de

WLSI-ASSID

E-Mail: iuliana.panchenko@assid.izm.fraunhofer.de

![]()